CPU-Simulator

This is a project required by Prof. Stephen Kaisler in Course: Computer System Architecture.

Purpose

To simulate a small classical CISC computer.

It has the following characteristics

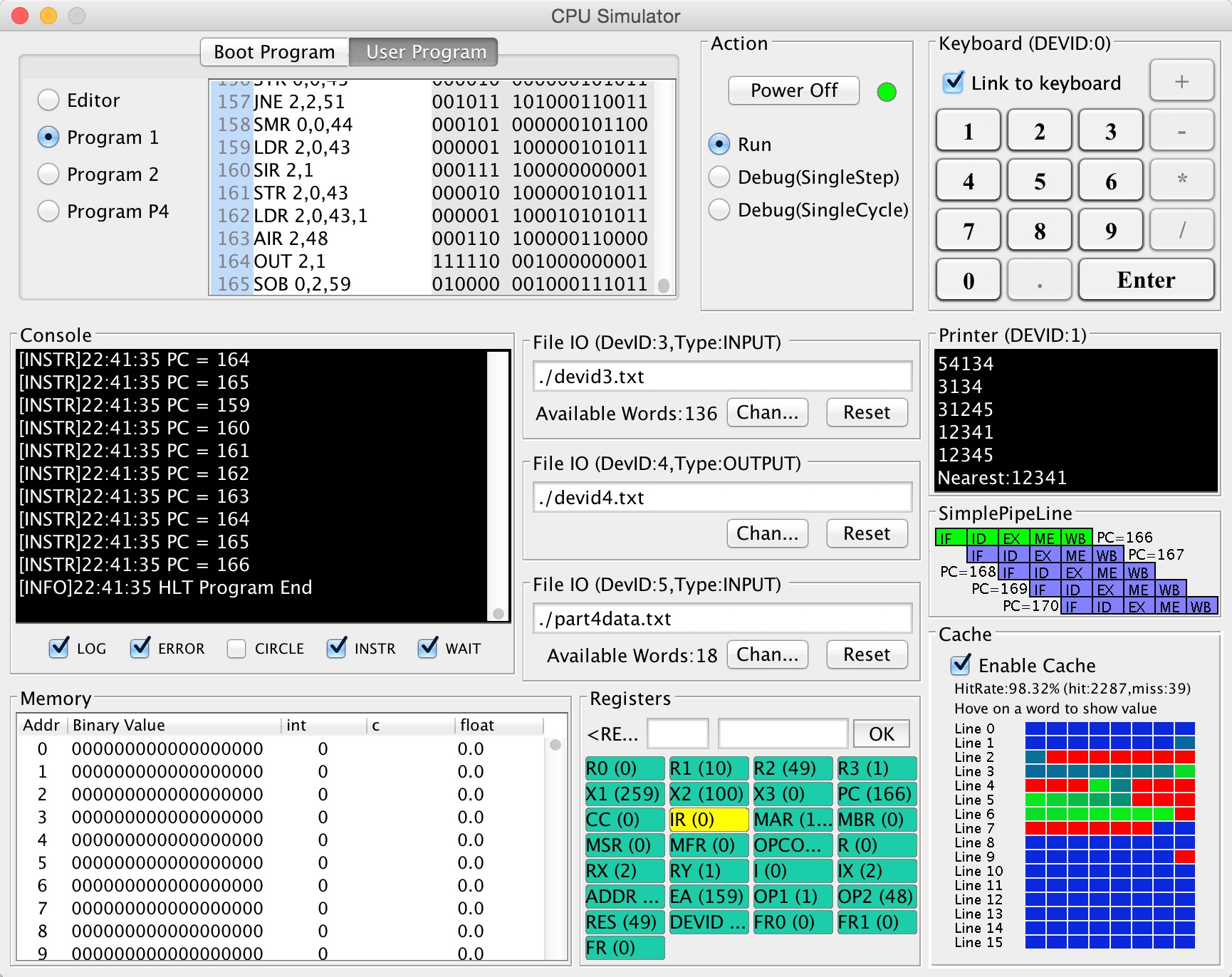

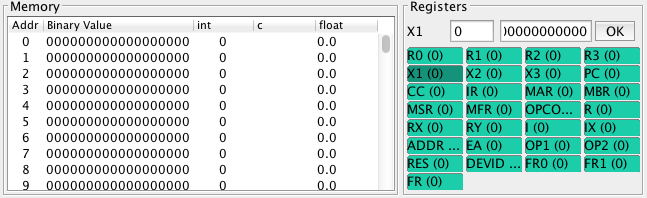

- Registers: General Purose Registers (GPRs), Index Registers, Program Counter, etc.

- 18-bit words

- Memory of 2048 words. (Size can be set in config file)

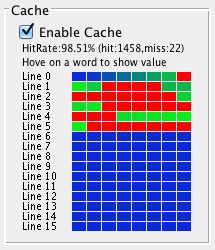

- Cache of 16 lines, each of which has 8 words. (line amount and capacity can also be set in config file)

Features

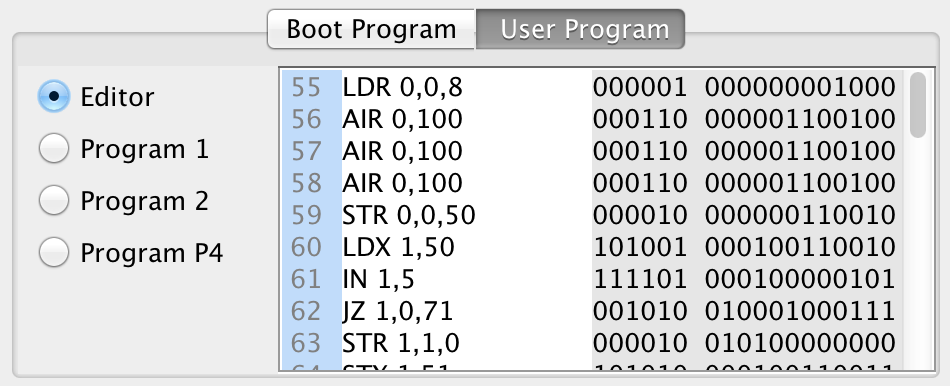

User Program Editor

Multiple Running Mode

CPU-Simulator can run the target program in 3 modes:

| Run: Simulator will run non-stoplly. |  |

|

| Debug (Single Step): Simulator will pause after each instruction finished. By clicking the Continue button, simulator will continue running. | ||

| Debug (Single Cycle): Simulator will pause after a cycle finished. By clicking the Continue button, simulator will continue running. |

Monitor for Memory and Registers

Cache Monitor

The panel shows the hit rate by coloring every block in cache lines. Green means that block gets an immediate hit and it turns blue gradually after a time during which it never get another hit.

With the 'Enable Cache' unchecked, CPU can access the main memory directly.

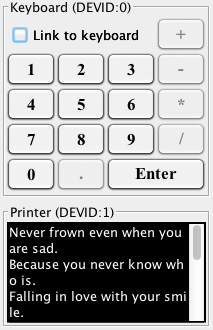

Input and Output Device

Design

Instructions

Memory

IO Devices

Screenshot